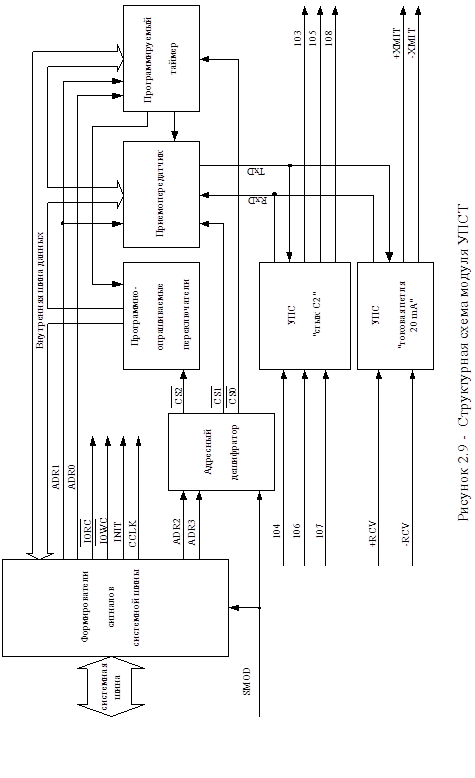

Основные узлы и модули комплекса КТСМ-01

Приемопередатчик модуля УПСТ реализован на БИС КР580ВВ51 (DD5) и предназначен для преобразования параллельного кода шины данных D0-D7, получаемого от центрального процессора, в последовательный поток символов со служебными битами и выдачи этого потока через устройство преобразования сигналов в последовательный канал связи с различной скоростью.

Приемопередатчик также предназначен для обратного преобразования последовательного потока символов в параллельное 8-ми разрядное слово. Передаваемая и принимаемая информация при необходимости может контролироваться на четность (нечетность). Режим работы микросхемы КР580ВВ51 может быть запрограммирован записью в соответствующие внутренние регистры слов инструкции режима, служебных синхросимволов и инструкции команды.

В модуле УПСТ приемопередатчик DD5 может работать только в асинхронном режиме. Асинхронный режим характеризуется одиночными посылками информации. В начале каждой посылки устанавливается отрицательный импульс «старт-бит», длительность которого равна биту данных, предназначенный для ввода в синхронизацию приемника.

В конце каждой посылки устанавливается положительный импульс «стоп-бит» (длительность может равняться 1, 1,5 или 2 длительностям бита информации), предназначенный для определения приемником конца посылки. Длительность «стоп-бита» устанавливается программно. Скорость приема / передачи данных задается инструкцией режима и может равняться 1/16 или 1/64 от частоты, поступающей на входы ТхС и RxC приемопередатчика.

После записи в микросхему данных в параллельном формате происходит автоматическое присоединение к каждой посылке старт-бита и стоп-бита. Бит контроля четности (если он запрограммирован) вводится перед битами останова и может иметь нулевое или единичное значение. Если в инструкции команды в разряд D0 записана «1» и на входе CTS установлено напряжение низкого уровня, то информация в виде последовательного потока данных подается на выход TxD со скоростью, равной 1/16 или 1/64 частоты синхронизации передатчика ТхС. Если микросхема не содержит информацию для передачи, то на выходе TxD устанавливается напряжение высокого уровня.

Напряжение высокого уровня на входе RxD свидетельствует о том, что в данный момент нет приема информации. Появление на входе RxD напряжения низкого уровня свидетельствует о приходе старт-бита. Истинность этого бита проверяется вторично стробированием в его середине. Если наличие напряжения низкого уровня на входе подтверждается, то запускается счетчик битов, который позволяет определить конец битов данных, бит контроля (если он запрограммирован) и стоп-бит. Если при вторичной проверке на входе RxD обнаруживается напряжение высокого уровня, то приемник переходит в исходное состояние.

Если в принятых данных присутствует ошибка, то внутренний триггер ошибки четности устанавливается в единичное состояние. Если при анализе стоп-бита на входе RxD обнаруживается напряжение низкого уровня, то триггер ошибки стоп-бита устанавливается в единичное состояние. Стоп-бит сигнализирует о том, что данные находятся в приемнике. Принятые данные передаются в выходной регистр данных, при этом на выходе RRDY появляется напряжение высокого уровня, сигнализируя о готовности к считыванию принятых данных. Если предыдущий символ не был считан процессором, то принятый символ замещает его в выходном регистре, а триггер ошибки переполнения устанавливается в единичное состояние. Наличие ошибок в триггерах не останавливает работу микросхемы, они могут быть считаны процессором и сброшены записью в приемопередатчик соответствующей инструкции.

Сигналы с выходов TRDY (передатчик готов) и RRDY (приемник готов) поступают через элемент DD8.3 на формирователь сигнала запроса прерывания INT. Элементы DD1.4 и DD1.3 предназначены для управлением светодиодными индикаторами «ПРИЕМ» и «ПЕРЕДАЧА».

Рекомендуем также:

Государственные структуры в морских портах, их назначение и функции

1. Администрации морских портов (АМП).

Администрации морских портов выполняют функции государственного надзора и контроля в морских портах, среди которых основными являются:

1) Обеспечение безопасности мореплавания в части:

– технической готовности судна к безопасному мореплаванию (проверяется ...

Принцип работы и характеристика устройств и агрегатов

Дизельный двигатель тепловоза преобразует энергию сгорания жидкого топлива в механическую работу вращения коленчатого вала, от которого вращение через тяговую передачу получают движущие колёса. К основным узлам тепловоза относится: экипажная часть, кузов тепловоза. К вспомогательным узлам — систем ...

Директивы ЕС в отношении предельных полных масс и осевых нагрузок АТС

Объемы международных автомобильных перевозок из стран Центральной Азии и Китая в страны Западной Европы, Прибалтики, России и Украины возрастают с каждым годом. По мнению специалистов, в ближайшие 10–15 лет их объем увеличится как минимум вдвое. Этому способствует строительство новых и расширение ...

Навигация

- Главная

- Сигнализации на железных дорогах

- Двигатели внутреннего сгорания

- Виды гидроусилителей

- Ремонт автомобильных шин

- Грузовые вагоны нового поколения

- Роль грузового автотранспорта

- Статьи